Intel da la campanada con su proceso litográfico Intel 18A: misma densidad en SRAM HD de 38 Mb/mm2 que TSMC con su N2

Ha sido en el ISSCC a puerta cerrada donde los grandes diseñadores de procesos litográficos han puesto en escena lo que no mostraron en el IEEE de este año. Intel y TSMC han acaparado todos los focos, Samsung no ha puesto en escena nada novedoso y Mediatek ha desvelado su TCAM, pero por encima de La entrada Intel da la campanada con su proceso litográfico Intel 18A: misma densidad en SRAM HD de 38 Mb/mm2 que TSMC con su N2 aparece primero en El Chapuzas Informático.

Ha sido en el ISSCC a puerta cerrada donde los grandes diseñadores de procesos litográficos han puesto en escena lo que no mostraron en el IEEE de este año. Intel y TSMC han acaparado todos los focos, Samsung no ha puesto en escena nada novedoso y Mediatek ha desvelado su TCAM, pero por encima de todos está Synopsys, puesto que ha logrado lo mismo que vamos a ver con TSMC e Intel, pero en vez de a 2 nm y 1,8 nm, ¡con 3 nm! ¿Cuál es el bombazo para nuestro sector? Pues el hecho de que Intel 18A tendrá una densidad en celdas SRAM HD de 38 Mb/mm2, es decir, iguala lo que ha hecho TSMC con su N2.

Hemos hablado largo y tendido de este tema, así que no queremos que sea algo extremadamente largo, puesto que faltan más datos y se tratará en su momento. Hay demasiada información específica cortesía de Ian Cutress, bastante técnico realmente, por parte de los cuatro implicados. Por ello, habrá una breve introducción para centrar tipos de celdas y el resto será el resumen de diapositivas, muy interesantes por cierto.

Celdas de tipo HP, HD y HC, todo lo que debes saber antes de entender las mejoras de Intel y TSMC

Dentro de las llamadas standard cells hay muchos tipos, quizás demasiados. Estas celdas son las encargadas de dar vida a los chips en su fabricación y según su tipo, función, rendimiento, densidad y consumo, se usan para unos tipos de chips u otros, por ejemplo, para CPU o GPU, dentro de todos los mercados disponibles.

Digamos que cada diseñador, sea el que sea, puede adaptarlas, les pone un nombre, unas características específicas y deja que su cliente, el diseñador del chip, elija la versión a usar para el diseño en concreto que quiera, simplificando la idea "muy mucho".

Las diapositivas de hoy y que vamos a ver a continuación, centrándonos en Intel y TSMC por ser los principales actores, y tocando de pasada a Mediatek y Synopsis por no dejarlos de lado dado que traen novedades interesantes, tocan dos tipos de celdas:

HP o High Performance -> Buscan el mejor rendimiento posible de la memoria caché (SRAM). Como características generales, suelen ser más altas, consumen más energía, logran mayores frecuencias y se usan en conjunto con la parte lógica de los chips en versiones de estos de alto rendimiento. Por dar un ejemplo, en CPU gaming, donde la frecuencia es clave.

HD o High Density -> Buscan, como su nombre indica, la mayor densidad de transistores por mm2. Son, lógicamente, celdas de menor tamaño general y frecuentemente debido a esa mayor densidad por unidad logran un menor consumo, así que su frecuencia es reducida. Se suelen usar en chips que buscan maximizar el tamaño de las cachés por diversos motivos, por ejemplo, CPU de servidor o algunas GPU concretas, aunque su uso puede ir incluso por gama de chips.

HC o High Current -> Están destinadas a los procesos litográficos y cachés que necesitan mayores corrientes de energía, normalmente usadas en las partes de la gestión de la potencia y como control de voltaje. Se diseñan para mantener la estabilidad de esa parte en contra de sus otras dos hermanas que buscan objetivos distintos.

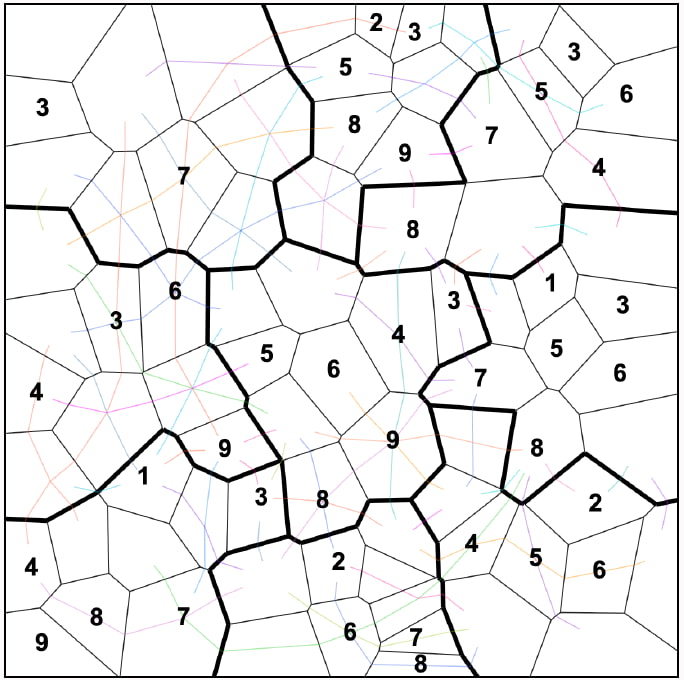

Con esto claro, siendo los tres tipos más usados (insisto en el hecho de que hay fácilmente 15 tipos más), tenemos todo más o menos situado para entender un poco más lo que han expuesto las 4 marcas. Como datos anexos, hay que entender que las celdas tienen diferentes agrupaciones de transistores (1T, 2T, 4T, 6T etc...) además, hay que tener en cuenta el tipo de transistor, ya que estamos en mitad de la transición de FinFET a GAA, de ahí el diagrama superior.

TSMC revela sus cartas y muestra su SRAM HD y HC para el N2 con aumentos interesantes

Comenzamos con el que había desvelado más información hasta la noche de ayer, donde el famoso número de 38 Mb/mm2 parecía inalcanzable. Pues bien, se vuelve a confirmar ese valor para las celdas HD, lo que supone nada menos que un aumento del 12% frente al N3, algo que los transistores GAA han permitido.

En cuanto a la versión HC, el aumento de densidad es del 18%, más impresionante si cabe. TSMC afirma que esto ha sido posible por su DTCO (Design Technology Co-Optimization), en otras palabras, optimizan la densidad según el diseño de la parte lógica del chip y la tecnología de fabricación y transistores. Sin embargo, no dan un valor en Mb/mm2 y nos dejan con las ganas de saber más.

El diseño de la SRAM es de tipo Double-pumped para AI y HPC en 6T (acertamos en su momento pese a las críticas de algunos) y mejora el rendimiento 1R1W (1-Read-1-Write) por ciclo. En cuanto a las de tipo HC, no hay mucho que comentar más que el hecho de que son de tipo Dual Tracking creadas con Nano Sheets y tienen una optimización del circuito que las lleva a conseguir un 6% más de densidad que en los 3 nm, a 100º C y 0,9 voltios en este N2.

En cuanto a la eficiencia, gracias a este sistema Double-pumped y todo lo dicho, en términos generales estamos hablando de una reducción de la potencia activa del 11% y una ganancia en la eficiencia general del 19%, lo cual es una barbaridad para este N2.

Todo con un Fmax del +6,3% bajo lo que TSMC denomina como TURBO ON en modo bypass, mientras que en TURBO OFF las celdas entran en un modo de Vmin donde reducen su voltaje. Esto es clave para optimizar el consumo en cualquier chip según cómo escale la frecuencia del mismo.

En definitiva y según lo mostrado por TSMC en sus Test Chip, sus celdas HD tienen un tamaño de 0,021 picómetros cuadrados tras todas las optimizaciones posibles (0,02625 µm² sin optimizar como adelantamos hace meses) en un tamaño de 256 MB.

En cuanto a sus HC, este tipo de celda con Fmax puede conseguir una impresionante frecuencia de 4,2 GHz a 1,05V o 4,5 GHz con 1,2V a 2 nm con NS, simplemente brutal, otro nivel, pero, ¿qué ha hecho Intel ante este despliegue técnico de su rival?

Intel da la sorpresa e iguala a TSMC con su nuevo nodo Intel 18A: celdas de alta densidad SRAM HD con 38 Mb/mm2

Pues sí, lo han logrado. Intel ha logrado igualar la densidad de TSMC en celdas HD para SRAM dando un puñetazo en la mesa, donde como hablábamos a principios de la semana pasada, logrará el mejor rendimiento, quedará por detrás en densidad lógica, pero igualará a su rival en densidad para la caché, lo cual le otorga un nodo más completo con este Intel 18A sobre el papel.

Intel denomina a sus celdas como HDC y HCC para diferenciarse en marketing de TSMC y sus rivales, pero lo dicho al principio de este artículo es igual de válido, solo le ponen una C al final y ya.

Lo importante aquí es la escalabilidad conseguida con ambos tipos de celdas, ya que para HDC se ha logrado una mejora de 0,88x pasando de 0,024 µm² a 0,021 µm² para HDC, y de 0,030 µm² a 0,023 µm² en HCC, con una escalabilidad de 0,77x.

Según Intel, han conseguido un mejor control de las Gate con menor variación en la lectura, lo que unido al hecho de que han eliminado el espaciamiento fin-to-fin da unas densidades como las que hemos visto, y donde también acertamos. Para descargo en este punto, dijimos que podían ser sin optimizar, y no, son ya optimizadas con su DTCO. Por ello, en vez de lograr los 47,62 Mb/mm2 que comentamos, Intel ha obtenido los mismos 38 Mb/mm2 que TSMC en este Intel 18A en celdas SRAM HD.

Parte de esta mejora es gracias a PowerVia, así que Intel juega con ventaja aquí realmente, puesto que TSMC no cuenta en este nodo con BSDPN mientras que los azules sí. Dicen que gracias a PowerVia han logrado un salto de densidad del 10%, con una caída del IR bastante resaltable, aunque no dan datos concretos realmente.

Sí dicen, en cambio, que PowerVia es usado en circuitos periféricos y en los array edges, optimizando las M2 a M4 (Frontside Grid).

De hecho, en el ejemplo que ponen a modo de Test Chip Intel mezcla celdas HDC y HCC en una configuración macro de 2.048x64 en la M4 donde afirman que el Vmin mejora en 100 mV para las primeras y 90 mV para las segundas. Si esto no te parece bastante impresionante, espera a ver la frecuencia: ¡5,6 GHz a 1,05V para celdas HCC!

Y claro, al dar este dato y no el de HDC, saltó la liebre, porque aquí tenemos un prototipo con 256b y una densidad de 34,1 Mb/mm2, lo cual es también brutal y va a complicar mucho la existencia a TSMC visto que no está lejos de la HD SRAM con sus 38 Mb/mm2 para Intel 18A.

Mediatek ofrece un paso adelante para switches y routers

No nos detendremos mucho aquí, puesto que esto está durando demasiado y, de momento, son más conceptos sin Test chip que otra cosa, habrá tiempo de profundizar más adelante. Mediatek ha ofrecido una memoria denominada como TCAM que está pensada en un principio para centros de datos de redes y ASIC, es decir Switch y router básicamente.

Según han mostrado es de tipo Two 6T-SRAM con transistores NMOS en pilas 4T, los cuales tienen la misma velocidad de lectura y escritura que las 6T nombradas. Mediatek ha mostrado su arquitectura básica y avanzada y resumiendo la primera, tendrán dos GIO generadores con un control global del clock para un único banco, lo que deja lugar a dos LIO con sus correspondientes entradas.

La avanzada, que debería ser la usada finalmente por Mediatek, está catalogada como DGSL TCAM, o Dynamically Gate Search-Line TCAM y evidentemente, es mucho más compleja. Desde el LCC con dos clock distintos, pasando por unos GIO mucho más avanzados y complejos con varios S1, así como unas entradas TCAM bastante más complejas con hasta 64 variables.

Faltan datos igualmente para aclarar el funcionamiento interno y el significado de las unidades. Sea como fuere, Mediatek asegura que en ML habrá un ahorro de energía del 16,7% si comparamos esta arquitectura DGSL con la Baseline comentada, mientras que en SL el ahorro llega hasta el 37,4%.

Teniendo en cuenta que hablamos de un Test Chip de 3 nm con una densidad de 4,97 Mb/mm2 y un voltaje de 0,75V a 2,2 GHz en 512e/220 bit, estamos hablando de un salto cualitativo para este sector tan específico y necesitado de él, puesto que switch y router requieren un paso adelante en SRAM sin lugar a dudas.

Synopsys da la sorpresa: iguala en densidad a Intel y TSMC, ¡en 3 nm!

Lo que ha publicado Synopsys es una serie de esquemas eléctricos más complejos todavía frente a los de Mediatek a modo de diagramas de flujo por buses en lo que han denominado como ERLS, o Extended Range Level Shifter. Lo que sabemos es que su SRAM será de tipo HD y tendrá dos interfaces de suministro eléctrico como base de la arquitectura.

Los tres buses principales serán ADD/WE, Control y Clock, donde cada uno integrará un ERLS doble entre VDD y VDDA. A partir de ahí todo se complica, porque el clock se divide en dos para terminar en la unidad de control lógico y en un driver WL. Cada vía se une de forma individual al CTRL y ADD/WE, y a partir de ahí el caos, porque el diagrama fluye hacia un BANK y un I/O Global.

A partir de ahí, lo realmente interesante es ver cómo funciona ERLS, porque lo principal es entender que elimina la contención que hay entre los transistores N y P, ahorrando área con transistores más grandes. Luego hablan de la integración de ERLS con Latch, el Clock Buffer con voltajes altos de tipo Bypass y las líneas VDDmin y VDDAmin para la interfaz Dual Rail.

Como se puede ver en las gráficas, el VDD se controla totalmente a 380 mV y el VDDA está casi siempre en los 540 mV, lo que genera un rango mucho más amplio, lo cual se ve perfectamente en el área de color verde.

Por último, en cuanto a datos generales, Synopsys afirma que logra una densidad en su SRAM HD de 38 Mb/mm2 para un chip fabricado a 3 nm ¡y en FinFET! Para entenderlo, es dejar en ridículo a TSMC e Intel. Aunque también es cierto que el rendimiento es muy inferior con solamente 2.325 MHz y a 25º C para un voltaje de 0.75V.

Es comprensible, seguramente a 2 nm o similar estaríamos hablando de una velocidad superior con una densidad algo más alta, pero no a las frecuencias que han mostrado Intel y TSMC, donde ahí sí que superan y por mucho a Synopsys.

La entrada Intel da la campanada con su proceso litográfico Intel 18A: misma densidad en SRAM HD de 38 Mb/mm2 que TSMC con su N2 aparece primero en El Chapuzas Informático.

![Los móviles con mejores cámaras [2025]](https://www.trecebits.com/wp-content/uploads/2024/03/moviles-con-mejores-camaras-150x150.jpg?#)

![[Actualización] Xbox está retirando los Alan Wake Remastered conseguidos de forma gratuita](https://www.somosxbox.com/wp-content/uploads/2023/12/alan-wake-2-somosxbox.jpeg)