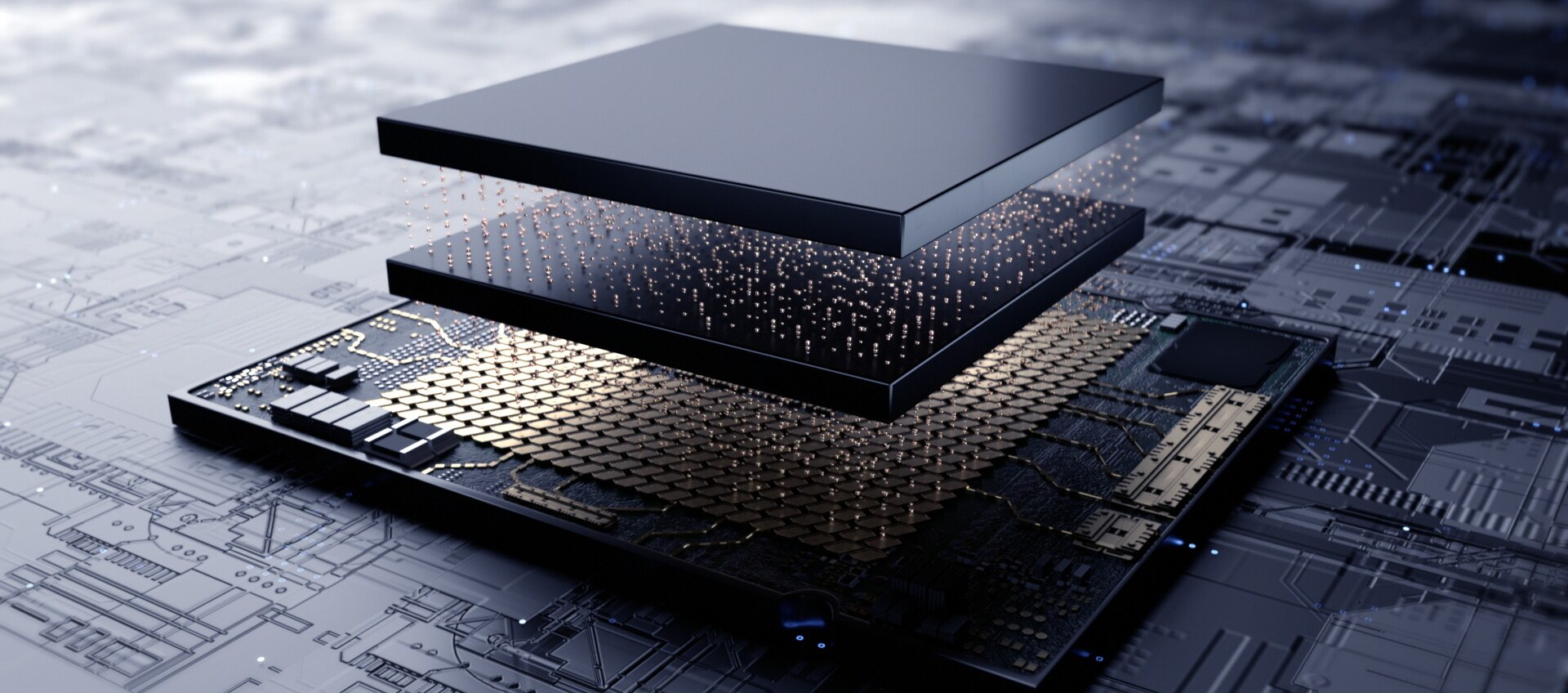

HBM4: nuove memorie a larghezza di banda elevata per AI e HPC

JEDEC ha pubblicato la specifica JESD270-4 per la nuova generazione di memorie HBM4, progettate per soddisfare i requisiti di prestazioni e densità richiesti da sistemi AI, data center e infrastrutture cloud avanzate. Ecco cosa cambia.

JEDEC, un’organizzazione globale di standardizzazione che definisce specifiche tecniche per semiconduttori e memorie elettroniche, promuovendo l’interoperabilità tra produttori e l’innovazione nell’industria, ha ufficializzato la nuova specifica HBM4 (High Bandwidth Memory 4). Pubblicata con l’appellativo JESD270-4, si tratta di un passo cruciale per soddisfare le crescenti esigenze computazionali dei data center moderni, dei sistemi di accelerazione AI e delle infrastrutture cloud di nuova generazione.

HBM4: architettura potenziata per performance estreme

Esaminando le nuove specifiche, appare evidente come HBM4 sia ponga sulla scia delle precedenti “iterazioni”, conservando la filosofia progettuale tipica delle memorie HBM: die DRAM impilati verticalmente e collegati tramite interconnessioni TSV (Through-Silicon Via).

La nuova generazione HBM4 introduce, tuttavia, una serie di innovazioni architetturali radicali, mirate a incrementare simultaneamente la larghezza di banda, la capacità e l’efficienza energetica.

Uno dei principali cambiamenti consiste nell’estensione del numero di canali indipendenti per stack, che passano da 16 di HBM3 ai 32 di HBM4. Questo schema non solo migliora la granularità nell’accesso ai dati, ma consente anche una maggiore parallelizzazione nelle operazioni di memoria, rendendo HBM4 particolarmente adatta ai carichi di lavoro particolarmente impegnativi tipici del deep learning e dell’analisi dei dati su larga scala.

In termini di capacità, HBM4 supporta configurazioni che arrivano fino a 64 GB per singolo stack. Ciò consente l’integrazione di quantità significative di memoria in spazi estremamente compatti, caratteristica essenziale per le GPU e gli acceleratori destinati all’addestramento dei modelli AI così come al calcolo scientifico.

Prestazioni e compatibilità

Con una velocità di trasferimento dati fino a 8 Gbps su un bus da 2048 bit, HBM4 può raggiungere una larghezza di banda aggregata fino a 2 TB/s per stack, un valore doppio rispetto ai limiti teorici delle memorie HBM3. L’introduzione di un bus separato per comandi e dati migliora l’elaborazione concorrente e assicura una latenza ridotta nelle operazioni multi-canale.

Inoltre, HBM4 mantiene retrocompatibilità con i controller HBM3, permettendo una transizione graduale per i produttori di chip e semplificando la progettazione di sistemi misti.

Efficienza energetica e gestione termica

L’efficienza energetica rappresenta un altro pilastro del nuovo standard. I produttori possono infatti scegliere tra diverse tensioni di alimentazione, con una flessibilità tale da poter mettere a punto configurazioni ottimizzate in funzione delle specifiche esigenze termiche ed energetiche del sistema.

In un’epoca in cui l’efficienza per Watt è un fattore sempre più critico, soprattutto nei supercomputer e nei cluster AI, questo tipo di controllo si traduce in un vantaggio competitivo tangibile.

Lo sviluppo di HBM4 è il risultato della collaborazione tra i principali attori del settore, tra cui Samsung, SK hynix e Micron, che hanno contribuito alla definizione dello standard e si preparano a commercializzare i primi prodotti compatibili già nel corso del 2025. Samsung, in particolare, ha annunciato l’intenzione di avviare la produzione per soddisfare le richieste di hyperscaler e produttori di chip AI.

Credit immagine in apertura: JEDEC

/https://www.ilsoftware.it/app/uploads/2024/06/YouTube-Music.jpg)

/https://www.ilsoftware.it/app/uploads/2023/06/OpenAI-Logo-GPT-ChatGPT-IA-min.jpg)

/https://www.html.it/app/uploads/2025/04/wp_drafter_547791.jpg)

.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/ILSOFTWARE-22.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/163.jpg)