TSMC SoW-X: cuando el silicio no es suficiente y el packaging es la verdadera innovación en los chips

¿Os acordáis del Tesla Dojo? Fue algo de lo que hablamos hace casi un año exacto, donde la compañía pretende unir 25 CPU en 1 para crear el mayor procesador de IA de la historia dedicado al entrenamiento de sus algoritmos para sus coches. En aquel momento ya hablamos de la tecnología que usarían para La entrada TSMC SoW-X: cuando el silicio no es suficiente y el packaging es la verdadera innovación en los chips aparece primero en El Chapuzas Informático.

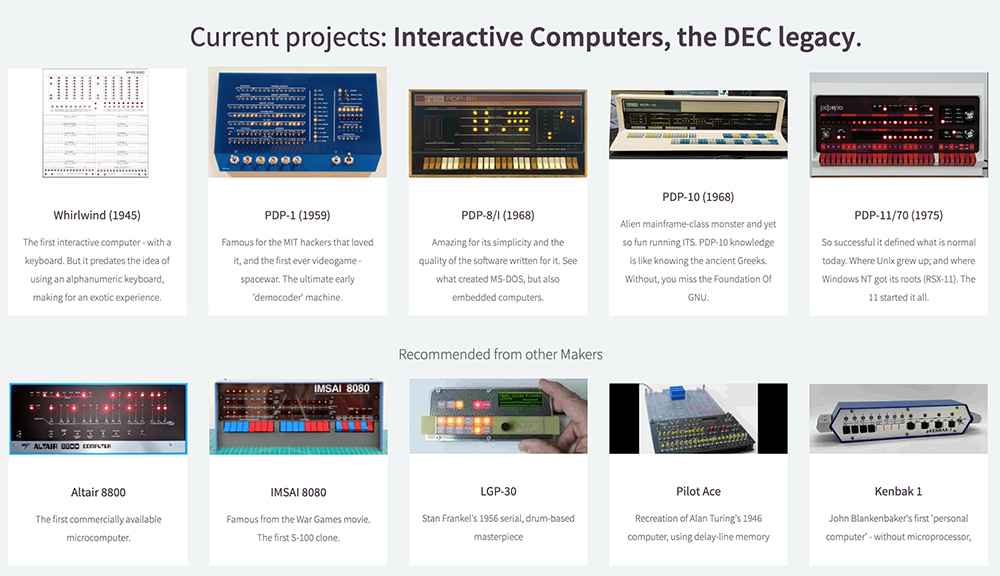

¿Os acordáis del Tesla Dojo? Fue algo de lo que hablamos hace casi un año exacto, donde la compañía pretende unir 25 CPU en 1 para crear el mayor procesador de IA de la historia dedicado al entrenamiento de sus algoritmos para sus coches. En aquel momento ya hablamos de la tecnología que usarían para conseguirlo, y de cómo TSMC lo haría posible: InFO-SoW. Pues bien, la compañía taiwanesa ha dado unos pocos datos más acerca de lo que será, y vendrá, posteriormente, siendo breve, pero concisa, al referenciar por primera vez a SoW-X como el futuro de los chips.

TSMC debe pasar página, no solo porque CoWoS ha sido ampliamente superado por Foveros 3D Direct, sino porque sus socios y clientes piden mucho más a la empresa de cara a la IA. Y aquí es donde en 2024 la compañía ya habló de SoW como el futuro, el cual, llegará dentro de dos años en su versión más avanzada.

TSMC SoW y SoW-X, una revolución que pretende sentar las bases del futuro de la IA

Sobra decir que esta tecnología de empaquetado a nivel de oblea no está destinada ni a CPU o GPU para consumo, sino más bien para servidores de alto rendimiento que necesitan solucionar problemas de consumo, espacio, diseño y costes. La compañía lo presentó ayer noche con el siguiente y breve comunicado:

TSMC continúa desarrollando su tecnología Chip on Wafer on Substrate (CoWoS) para abordar la insaciable necesidad de la IA de más lógica y memoria High Bandwidth Memory (HBM). La compañía planea producir CoWoS con un tamaño de retícula de 9,5 en 2027, lo que permitirá la integración de 12 o más pilas HBM en un paquete, junto con la tecnología lógica de vanguardia de TSMC.

Tras presentar su revolucionaria tecnología System-on-Wafer (TSMC-SoW) en 2024, TSMC continuó con SoW-X , una solución basada en CoWoS para crear un sistema del tamaño de una oblea con una potencia de procesamiento 40 veces superior a la solución CoWoS actual. La producción en serie está prevista para 2027.

Un tamaño de retícula 40 veces mejor que puede llegar a soportar un consumo para la oblea de 15.000W

Y no es una cifra baladí, es precisamente lo que la propia Tesla comentó en su momento, y de hecho, podría ser algo mejor finalmente. TSMC no ha querido revelar demasiados detalles, pero para entender la innovación que representa se valor de 40 retículas, hay que entender primero qué es una retícula.

TSMC hace referencia a esta como la unidad de área máxima que se puede imprimir mediante un sistema fotolitográfico en un solo shoot a la hora de fabricar un chip cualquiera. Sabiendo esto, y viendo la imagen facilitada por TSMC, podemos entender que pasar de una retícula de 3,3x con 8 pilas de HBM para un sustrato de 80x80 mm se considera como "base", o principio de partida, y que el año que viene con CoWoS SoIC pasaremos a nada menos que una retícula de 5,5X con 12 stack de HBM en un tamaño de 100x100 mm, de ahí que la potencia relativa aumente a 3,5X.

Pues bien, como ha dicho TSMC, y ha actualizado, ya que en la imagen del 2024 se muestran datos peores, en 2027 habrán conseguido un tamaño de retícula de 9,5X, lo que supone un sustrato mayor a ese 120x120 mm, concretamente, 120x150 mm, con una potencia relativa de 7X.

Y el colofón es SoW y SoW-X, donde de este último solo sabemos que la potencia pasará a 40X frente a la base de 2023 con un tamaño de retícula de 40X con 60 stacks de HBM. Por último, hay que entender otro detalle importante: SoW y SoW-X no son exactamente iguales, el primero usa inFO-SoW, el segundo se basa en CoW-SoW.

Cerebras System fue el primer chip en oblea exitoso con SoW

O lo que es igual, habrá una versión sin interposer con RDL, más barata (InFO-SoW) y posteriormente llegará la versión en 3D con TSV y SoIC que debería ser la realmente interesante (CoW-SoW-X). Esto es un paso tremendo hacia delante que puede eclipsar a Intel dentro del sector de la IA, puesto que, al menos por ahora, no tienen nada que pueda competir hasta este extremo.

De hecho, la primera integración exitosa de TSMC la hizo con Cerebras System mediante un packaging de tipo SoW para incluir hasta 850.000 núcleos en un área de 46.225 mm2 en 7 nm, así que realmente tienen experiencia en estos diseños, y lo llevarán al siguiente nivel en dos años, en los que sabremos mucho más.

La entrada TSMC SoW-X: cuando el silicio no es suficiente y el packaging es la verdadera innovación en los chips aparece primero en El Chapuzas Informático.