Cómo hacer un buen Makefile

Cómo hacer tu primer Makefile Make es una herramienta de automatización que simplifica el proceso de compilación y vinculación de proyectos de software. Al definir las relaciones entre tus archivos fuente y los comandos necesarios para transformarlos en un ejecutable, Make puede determinar automáticamente qué partes de tu programa necesitan ser reconstruidas, ahorrándote tiempo y reduciendo errores. Si estás dando tus primeros pasos en el desarrollo de software o quieres mejorar tus habilidades de automatización, dominar Make puede ser una de las inversiones más valiosas para tu flujo de trabajo. ¿Qué es un Makefile y por qué utilizarlo? Un Makefile es simplemente un archivo de texto que contiene un conjunto de instrucciones para el programa make. Estas instrucciones le indican a Make: Qué archivos debe compilar En qué orden debe hacerlo Qué dependencias existen entre esos archivos Qué comandos ejecutar para producir el resultado final ¿Qué nombre darle a tu Makefile? Por defecto, Make busca un archivo llamado GNUmakefile, makefile o Makefile (en ese orden). La convención recomendada es usar Makefile (con "M" mayúscula), ya que aparece destacado en listados de directorios junto a archivos como README. Componentes básicos de un makefile El núcleo de todo Makefile son las reglas, que le indican a Make cómo construir objetivos (targets) a partir de sus prerrequisitos (prerequisites). Una regla generalmente tiene tres partes: Objetivo (Target): El archivo que quieres crear o actualizar, como un ejecutable o un archivo objeto. Prerrequisitos (Prerequisites): Los archivos de los que depende el objetivo. Si alguno de estos cambia, el objetivo necesita ser reconstruido. Receta (Recipe): Los comandos que Make ejecuta para construir el objetivo a partir de sus prerrequisitos. # Estructura básica de una regla # objetivo: prerrequesitos # receta (debe estar indentada con un ¡¡tabulador!!) hello: hello.c cc -o hello hello.c Cómo Make evalúa las reglas Cuando ejecutas make target, ocurre lo siguiente: Make busca la regla para ese target Examina si los prerrequisitos existen Si algún prerrequisito no existe, busca reglas para crearlo primero Compara las fechas de modificación del target y sus prerrequisitos Si el target no existe, lo construye Si algún prerrequisito es más reciente que el target, reconstruye el target Ejecuta la receta si determinó que el target necesita ser reconstruido Usando variables para un código más limpio Para hacer que tu Makefile sea más fácil de mantener, especialmente cuando el número de archivos fuente crece, es útil usar variables. Por ejemplo, puedes definir una variable para la lista de archivos objeto, el compilador o los flags. CC = cc CFLAGS = -Wall -Wextra -Werror OBJS = main.o utils.o hello.o hello: $(OBJS) $(CC) $(CFLAGS) -o hello $(OBJS) Targets predefinidos comunes en Makefiles Los Makefiles suelen incluir targets predefinidos que facilitan la gestión del proceso de construcción de un proyecto. Estos targets son convenciones aceptadas en la comunidad de desarrollo y ayudan a estandarizar tareas repetitivas. A continuación, te explico los más comunes: all, clean, fclean y re, junto con la regla .PHONY.PHONY all El target all es el objetivo predeterminado que se ejecuta cuando simplemente escribes make en la terminal sin especificar un target. Su propósito es compilar todo el proyecto, generando todos los ejecutables, bibliotecas o dependencias necesarias. Por lo general, all depende de otros targets que representan los componentes principales del proyecto (como ejecutables o bibliotecas). Make se encarga de verificar que todas estas dependencias estén actualizadas y construidas. Simplifica el proceso de compilación completa con un solo comando. all: program1 program2 clean El target clean elimina los archivos generados durante la compilación, como archivos objeto (.o), ejecutables o archivos temporales. Su objetivo es limpiar el directorio, dejando solo los archivos fuente y de configuración. Define una receta que elimina los archivos especificados. No depende de otros targets, ya que su función es independiente. Permite empezar de cero o evitar problemas causados por archivos residuales en una nueva compilación. clean: rm -f *.o program1 program2 fclean (full clean) Similar a clean, pero más completo. Mientras que clean puede limitarse a eliminar archivos intermedios (como .o), fclean suele borrar también los ejecutables o bibliotecas generadas, dejando el proyecto en un estado completamente limpio. A menudo depende de clean para realizar una limpieza inicial y luego agrega comandos adicionales para eliminar los artefactos finales. Ideal para una limpieza profunda antes de una reconstrucción completa. fclean: clean rm -f program1 program2 re (rebuild) El target re fuerza

Cómo hacer tu primer Makefile

Make es una herramienta de automatización que simplifica el proceso de compilación y vinculación de proyectos de software. Al definir las relaciones entre tus archivos fuente y los comandos necesarios para transformarlos en un ejecutable, Make puede determinar automáticamente qué partes de tu programa necesitan ser reconstruidas, ahorrándote tiempo y reduciendo errores.

Si estás dando tus primeros pasos en el desarrollo de software o quieres mejorar tus habilidades de automatización, dominar Make puede ser una de las inversiones más valiosas para tu flujo de trabajo.

¿Qué es un Makefile y por qué utilizarlo?

Un Makefile es simplemente un archivo de texto que contiene un conjunto de instrucciones para el programa make. Estas instrucciones le indican a Make:

- Qué archivos debe compilar

- En qué orden debe hacerlo

- Qué dependencias existen entre esos archivos

- Qué comandos ejecutar para producir el resultado final

¿Qué nombre darle a tu Makefile?

Por defecto, Make busca un archivo llamado GNUmakefile, makefile o Makefile (en ese orden). La convención recomendada es usar Makefile (con "M" mayúscula), ya que aparece destacado en listados de directorios junto a archivos como README.

Componentes básicos de un makefile

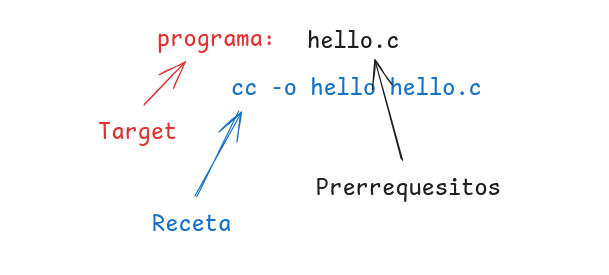

El núcleo de todo Makefile son las reglas, que le indican a Make cómo construir objetivos (targets) a partir de sus prerrequisitos (prerequisites). Una regla generalmente tiene tres partes:

- Objetivo (Target): El archivo que quieres crear o actualizar, como un ejecutable o un archivo objeto.

- Prerrequisitos (Prerequisites): Los archivos de los que depende el objetivo. Si alguno de estos cambia, el objetivo necesita ser reconstruido.

- Receta (Recipe): Los comandos que Make ejecuta para construir el objetivo a partir de sus prerrequisitos.

# Estructura básica de una regla

# objetivo: prerrequesitos

# receta (debe estar indentada con un ¡¡tabulador!!)

hello: hello.c

cc -o hello hello.c

Cómo Make evalúa las reglas

Cuando ejecutas make target, ocurre lo siguiente:

- Make busca la regla para ese target

- Examina si los prerrequisitos existen

- Si algún prerrequisito no existe, busca reglas para crearlo primero

- Compara las fechas de modificación del target y sus prerrequisitos

- Si el target no existe, lo construye

- Si algún prerrequisito es más reciente que el target, reconstruye el target

- Ejecuta la receta si determinó que el target necesita ser reconstruido

Usando variables para un código más limpio

Para hacer que tu Makefile sea más fácil de mantener, especialmente cuando el número de archivos fuente crece, es útil usar variables. Por ejemplo, puedes definir una variable para la lista de archivos objeto, el compilador o los flags.

CC = cc

CFLAGS = -Wall -Wextra -Werror

OBJS = main.o utils.o hello.o

hello: $(OBJS)

$(CC) $(CFLAGS) -o hello $(OBJS)

Targets predefinidos comunes en Makefiles

Los Makefiles suelen incluir targets predefinidos que facilitan la gestión del proceso de construcción de un proyecto. Estos targets son convenciones aceptadas en la comunidad de desarrollo y ayudan a estandarizar tareas repetitivas. A continuación, te explico los más comunes: all, clean, fclean y re, junto con la regla .PHONY.PHONY

all

El target all es el objetivo predeterminado que se ejecuta cuando simplemente escribes make en la terminal sin especificar un target. Su propósito es compilar todo el proyecto, generando todos los ejecutables, bibliotecas o dependencias necesarias.

Por lo general, all depende de otros targets que representan los componentes principales del proyecto (como ejecutables o bibliotecas). Make se encarga de verificar que todas estas dependencias estén actualizadas y construidas.

Simplifica el proceso de compilación completa con un solo comando.

all: program1 program2

clean

El target clean elimina los archivos generados durante la compilación, como archivos objeto (.o), ejecutables o archivos temporales. Su objetivo es limpiar el directorio, dejando solo los archivos fuente y de configuración.

Define una receta que elimina los archivos especificados. No depende de otros targets, ya que su función es independiente.

Permite empezar de cero o evitar problemas causados por archivos residuales en una nueva compilación.

clean:

rm -f *.o program1 program2

fclean (full clean)

Similar a clean, pero más completo. Mientras que clean puede limitarse a eliminar archivos intermedios (como .o), fclean suele borrar también los ejecutables o bibliotecas generadas, dejando el proyecto en un estado completamente limpio.

A menudo depende de clean para realizar una limpieza inicial y luego agrega comandos adicionales para eliminar los artefactos finales.

Ideal para una limpieza profunda antes de una reconstrucción completa.

fclean: clean

rm -f program1 program2

re (rebuild)

El target re fuerza la reconstrucción completa del proyecto. Primero limpia todos los archivos generados y luego recompila todo desde cero.

Depende de clean o fclean para eliminar archivos existentes y de all para reconstruir el proyecto. Es una combinación de limpieza y compilación en un solo paso.

Perfecto para cuando haces cambios importantes en el código o la configuración y necesitas asegurarte de que todo se reconstruya correctamente.

re: fclean all

.PHONY

.PHONY es una directiva especial de Make que indica que ciertos targets no corresponden a archivos reales. Por defecto, Make asume que un target representa un archivo y solo ejecuta su receta si el archivo no existe o está desactualizado. Sin embargo, targets como all, clean, fclean y re no generan archivos, son solo nombres para ejecutar comandos.

Al declarar un target como .PHONY, Make ignora la existencia de archivos con ese nombre y siempre ejecuta la receta cuando se invoca el target.

Evita comportamientos inesperados. Por ejemplo, si hay un archivo llamado clean, sin .PHONY, Make podría pensar que el target clean ya está actualizado y no ejecutaría la limpieza. Con .PHONY, esto no sucede.

.PHONY: all clean fclean re

Variables automáticas y wildcards en Make

En Make, las variables automáticas y los wildcards son herramientas fundamentales que facilitan la creación de Makefiles eficientes y flexibles, especialmente en proyectos con múltiples archivos.

Wildcards en Make: * y %

Make emplea dos tipos de wildcards: * y %. Aunque ambos son poderosos, tienen significados y usos distintos que es importante distinguir.

Wilcard *

El wildcard * busca en el sistema de archivos nombres de archivos que coincidan con un patrón. Por ejemplo, *.c encuentra todos los archivos con extensión .c en el directorio actual.

Siempre envuelve * en la función $(wildcard ...). Esto asegura que se expanda correctamente y evita problemas comunes.

Si usas * directamente en una variable sin $(wildcard ...), no se expandirá y quedará como el literal "*.o".

Si * no encuentra archivos coincidentes, permanece sin cambios (a menos que esté dentro de $(wildcard ...)), lo que puede generar errores inesperados.

# Uso incorrecto

wrong: *.o

# Uso correcto

right: $(wildcard *.o)

Wildcard %

El wildcard % se usa en reglas de patrones para coincidir y reemplazar partes de nombres de archivos. No busca en el sistema de archivos, sino que trabaja con cadenas dentro del Makefile.

Modo de coincidencia: % encuentra una parte de la cadena (llamada stem) en reglas de patrones.

Modo de reemplazo: Usa el stem coincidente para construir nuevos nombres de archivos.

Es común en reglas de patrones (como %.o: %.c) y reglas estáticas.

# % coincide con el nombre del archivo, por ejemplo main.o depende de main.c

%.o: %.c

cc -c $< -o $@

Variables Automáticas en Make

Las variables automáticas son variables predefinidas que Make asigna automáticamente con información sobre el target y sus prerrequisitos al ejecutar una regla. Son ideales para escribir recetas genéricas y adaptables.

Variables automáticas comunes

- $@: El nombre del target actual.

- $<: El primer prerrequisito de la regla.

- $^: La lista completa de prerrequisitos.

- $?: La lista de prerrequisitos más recientes que el target.

all: program1 program2

echo $@

# imprime el nombre del target -> "all"

echo $?

# imprime los prerrequesitos más recientes del target

echo $^

# imprime todos los prerrequesitos ->"program1 program2"

echo $<

# imprime el primer prerrequesito ->"program1"

Estas variables eliminan la necesidad de escribir nombres específicos en las recetas, haciendo que las reglas sean reutilizables.

Combinando wildcards y variables automáticas

La combinación de wildcards y variables automáticas permite manejar múltiples archivos de manera eficiente. Veamos un ejemplo para compilar varios archivos .c a .o

%.o: %.c

cc -c $< -o $@

# % se usa para coincidir cada archivo .c con su correspondiente .o

# compilando el fuente con $< y el objetivo con $@

Ejemplo completo de Makefile

# Compilador y flags

CC = cc

CFLAGS = -Wall -Wextra -Werror

# Archivos

SRCS = $(wildcard *.c)

OBJS = $(SRCS:%.c=%.o)

TARGET = push_swap

# Reglas principales

all: $(TARGET)

$(TARGET): $(OBJS)

$(CC) $(CFLAGS) $^ -o $@

@echo "✅ Compilación completada: $@"

clean:

rm -rf $(OBJS)

@echo "

![Apple to Craft Key Foldable iPhone Components From Liquid Metal [Kuo]](https://www.iclarified.com/images/news/96784/96784/96784-640.jpg)

![Apple to Focus on Battery Life and Power Efficiency in Future Premium Devices [Rumor]](https://www.iclarified.com/images/news/96781/96781/96781-640.jpg)

_Federico_Caputo_Alamy.jpg?#)

![[The AI Show Episode 139]: The Government Knows AGI Is Coming, Superintelligence Strategy, OpenAI’s $20,000 Per Month Agents & Top 100 Gen AI Apps](https://www.marketingaiinstitute.com/hubfs/ep%20139%20cover-2.png)

![[The AI Show Episode 138]: Introducing GPT-4.5, Claude 3.7 Sonnet, Alexa+, Deep Research Now in ChatGPT Plus & How AI Is Disrupting Writing](https://www.marketingaiinstitute.com/hubfs/ep%20138%20cover.png)

![From hating coding to programming satellites at age 37 with Francesco Ciulla [Podcast #165]](https://cdn.hashnode.com/res/hashnode/image/upload/v1742585568977/09b25b8e-8c92-4f4b-853f-64b7f7915980.png?#)

.jpg?width=1920&height=1920&fit=bounds&quality=80&format=jpg&auto=webp#)

.png?#)