Intel muestra sus CPU Panther Lake con una disposición de cachés peculiar: más L2 total que L3, el doble de GAP que Lunar Lake, el triple que Arrow Lake

Intel se adelantó al día de mañana y no quiso dejar pasar la oportunidad de mostrar en su stand las CPU Panther Lake en todo su esplendor, que sin ser la primera vez que las vemos, sí que dejó un sistema de prueba funcional donde se vieron algunas curiosidades interesantes, aunque por desgracia, nada del La entrada Intel muestra sus CPU Panther Lake con una disposición de cachés peculiar: más L2 total que L3, el doble de GAP que Lunar Lake, el triple que Arrow Lake aparece primero en El Chapuzas Informático.

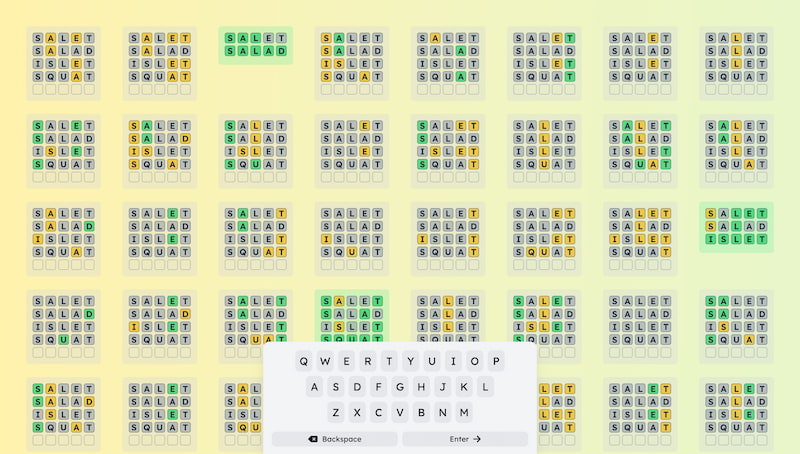

Intel se adelantó al día de mañana y no quiso dejar pasar la oportunidad de mostrar en su stand las CPU Panther Lake en todo su esplendor, que sin ser la primera vez que las vemos, sí que dejó un sistema de prueba funcional donde se vieron algunas curiosidades interesantes, aunque por desgracia, nada del rendimiento como tal. Lo más curioso sin duda fue el tema de las cachés, puesto que Panther Lake mostró más L2 total que L3, siendo algo que, en principio, podría desconcertar a más de uno por la distancia en capacidad entre ellas, la mayor registrada.

Panther Lake como arquitectura tiene dos objetivos fundamentales para lograr afianzarse en el liderato, al menos momentáneo, frente a AMD y Qualcomm: la eficiencia de Lunar Lake con el rendimiento de Arrow Lake. Parece sencillo, ¿no? Dale una vuelta mental a la frase, porque conseguir el rendimiento de escritorio en un tercio del consumo, para portátiles, no es cualquier tontería.

Intel Panther Lake es visto con unas cachés L2 y L3 dispares

Es algo que va a dar de qué hablar, más allá de haber quitado el HT como ya pasó con las dos generaciones comentadas arriba, y que de nuevo, no estará presente en portátiles. La microarquitectura Cougar Cove y Darkmont para P-Cores y E-Cores van a suponer un salto adelante más que interesante, pero lo visto en el COMPUTEX 2025 siembra ciertas dudas sobre la disposición de cachés que usan.

Intel exhibió un RVP y un kit de desarrollo donde se podía ver una placa base con un disipador de cobre y un pequeño ventilador, dando a entender de que refrigerar estas CPU no será demasiado difícil, pero claro, lo que mostraron fue un ES, que al parecer, estaba capado.

Y lo sabemos porque en el entorno de prueba se le pudo ver a esta CPU en concreto funcionar a una frecuencia base de solo 2 GHz y un Boost de 3 GHz, cuando se esperan velocidades sobre los 5 GHz o superiores, y claro, nadie se pudo resistir a mirar otros datos anexos como la NPU 6 o la GPU Xe3 Celestial...

Sin encontrar nada reseñable. En cambio, la CPU y sus cachés sí que dieron juego.

Las diferencias se amplían: más del doble que Lunar Lake, más del triple que Arrow Lake

Los cambios son gigantescos en el apartado de caché, y eso revela mucho de lo que podremos esperar en cuanto a rendimiento, recordemos, que parar portátiles.

Lo que se vio fue una L2 total de 24 MB y una L3, muy "pequeña" de 18 MB. A esto hay que añadir los datos de los tres SKU que Intel lanzará al mercado y que recogemos de la última filtración que vimos en febrero con todo lujo de detalles, para dar contexto a la teoría, que no práctica, posterior:

- PTL-H (gama alta) -> 4+8+4+12, x8 G4 x4 G5, 4x TBT4, LPDDR5x (7.467 o 8.533 MT/s), 180 TOPS (10+50+120) para 25 vatios de consumo en PL1, 45W en PL2.

- PTL-H (gama media) -> 4+8+4+4, x8 G4 x12 G5, 4x TBT4, LPDDR5x (7.467 o 8.533 MT) & DDR5 (7.200 MT/s), 100 TOPS (10+50+40) para 25 vatios de consumo en PL1, 45W en PL2.

- PTL-H (gama baja) -> 4+0+4+4, x8 G4 x4 G5, 4x TBT4, LPDDR5x (6.800 MT) & DDR5 (6.400 MT), 100 TOPS (10+50+40) para solo 25W de consumo en PL1, 45W en PL2.

¿Cómo se van a repartir las cachés para cada microarquitectura? Partiendo de la base de que hablamos de la configuración más alta en núcleos, obtenemos en total 16 con 16 hilos para 4+8+4. Lo que se especula, y parece bastante razonable, es que las disposiciones de L2 y L3 son las siguientes:

- L2 de 24 MB -> 3 MB por cada P-Core más 2 x 4 MB para cada clúster de E-Core y 4 MB para el clúster de LPE Cores.

- L3 de 18 MB -> 3 MB por cada P-Core más 2 x 3 MB por cada clúster de E-Core.

A esto habría que sumarla la supuesta SLC de 8 MB que integrará cada CPU. Esto supone duplicar la distancia entre L2 y L3 que había en Lunar Lake, y triplicar la que había en Arrow Lake entre estas cachés para las CPU más rápidas que puso Intel en el mercado (Intel Core Ultra 9 288V con 14+12 y Core Ultra 9 285K con 40+36 MB respectivamente).

Por lo tanto, Intel amplía la distancia empujando la L2 hacia arriba más que la L3, lo que sugiere un importante salto de IPC, en teoría, de dos dígitos. Sea como fuere, quedan pocos meses para su presentación oficial y lanzamiento, aunque en masa llegarán a principios del año que viene.

La entrada Intel muestra sus CPU Panther Lake con una disposición de cachés peculiar: más L2 total que L3, el doble de GAP que Lunar Lake, el triple que Arrow Lake aparece primero en El Chapuzas Informático.