Intel responde a TSMC y su SoW-X mostrando sus nuevos packaging EMIB-T 2.5D, Foveros-R y Foveros-B, así como Foveros Direct 3D

Lo que vimos la semana pasada con TSMC y su SoW y SoW-X dejó perplejo al mundo, y como era de esperar, Intel en su evento Direct Connect 2025 ha respondido, y de qué manera. No solamente contesta a su gran rival poniendo sobre la mesa 4 tecnologías evolucionadas de las actuales, sino que consigue La entrada Intel responde a TSMC y su SoW-X mostrando sus nuevos packaging EMIB-T 2.5D, Foveros-R y Foveros-B, así como Foveros Direct 3D aparece primero en El Chapuzas Informático.

Lo que vimos la semana pasada con TSMC y su SoW y SoW-X dejó perplejo al mundo, y como era de esperar, Intel en su evento Direct Connect 2025 ha respondido, y de qué manera. No solamente contesta a su gran rival poniendo sobre la mesa 4 tecnologías evolucionadas de las actuales, sino que consigue dejar en pañales los datos de los de Taiwán. Por ello, conviene conocer hacia dónde van los azules con los nuevos packaging EMIB-T 2.5D, Foveros-R, Foveros-B y Foveros Direct 3D.

Posiblemente, el más conocido por todos sea el último, que curiosamente es el más avanzado y será crucial para el Base Tile basado en el PDK de Intel 18A-PT, que recibirá en su momento otro nombre, y por supuesto, Intel 14A e Intel 14A-E, los cuales hemos visto en el artículo de esta mañana en profundidad. Sea como fuere, es una estrategia a dos bandas, donde por un lado se impulsan los nodos, mientras que por otro lado va al packaging, muy al estilo de TSMC, pero más completo y ambicioso.

Intel muestra sus nuevo roadmap para packaging y deja a todos asombrados

Lo presentado es bastante disruptivo y tiene sus pros y sus contras, pero el enfoque general parece mucho mejor que el de TSMC, por decirlo de alguna manera, parece menos "exclusivo". Para entenderlo, haremos un breve resumen de lo que tiene Intel en el mercado ahora mismo y que deberíamos conocer de antemano, puesto que los hemos desgranado hasta la saciedad.

De menos complejo y con menos opciones de stacking tenemos FCBGA 2D y 2D+, seguido de EMIB-M 2.5D y Foveros-S.

El equivalente al primero en TSMC sería InFO, para el segundo sería CoWoS y para el tercero SoIC-X, pero la realidad es que no llegan a ser tan completos y complejos como las opciones de Intel, pero sí algo más baratas de producir, y en volumen.

Los azules captaron el mensaje de sus socios, ya que quieren atraerlos para quitarles cuota de mercado a TSMC y ofrecerles sus nodos, creando un ecosistema tal y como tienen los taiwaneses, y para ello, debían mejorar en las dos áreas donde estaban fallando. Ahí entran estas nuevas versiones de los packaging existentes.

EMIB-T 2.5D, la respuesta a TSMC SoW-X para IA

Crecimiento modular, este sería el gran titular que podemos extraer de lo que ha presentado Intel, pero antes debemos tener claro que es EMIB como tecnología en su concepto. Esta no es más que una forma de interconectar chiplets (dies) mediante un puente de silicio en el sustrato, de ahí su nombre (Embedded Multi-die Interconnect Bridge), y tiene la ventaja de hacerlo de forma horizontal (importante) sin necesidad de usar un interposer como requiere CoWoS de TSMC.

¿Qué ha hecho Intel con EMIB-T 2.5D? Pues ha convertido lo horizontal en vertical (solo para entregar la energía) mediante TSV usando condensadores de tipo MIM (Metal-Insulator-Metal) para estabilizar el voltaje bajo cada die, reduciendo su consumo energético. O lo que es igual, a las opciones de interconectar dies de forma horizontal ahora también permite hacerlo de forma vertical, con un menor consumo de energía y para colmo, haciéndolo compatible con HBM4.

Esto es posible debido a la reducción de ruido eléctrico, tanto DC como AC, por todo lo dicho, lo cual permite conseguir la compatibilidad y sostenibilidad de las altas velocidades necesarias para HBM4, no es un problema de formato, pines o similar, es simple velocidad y estabilidad de las señales para con el voltaje. Esto está fantástico, pero, ¿qué tiene que ver con SoW-X llegados a este punto? La escalabilidad, ese crecimiento modular que hablamos al principio de este apartado.

Lo que planea Intel es un concepto similar al de TSMC, pero en función realmente es distinto. Intel planea escalar EMIB-T 2.5D mediante la interconexión de múltiples chiplets (dies) con memorias HBM4 en un mismo packaging a base de ampliar el tamaño de la retícula, algo de lo que hablamos largo y tendido con SoW-X en su correspondiente artículo.

De 2023 a 2028 se escalará 12 veces el tamaño de la retícula

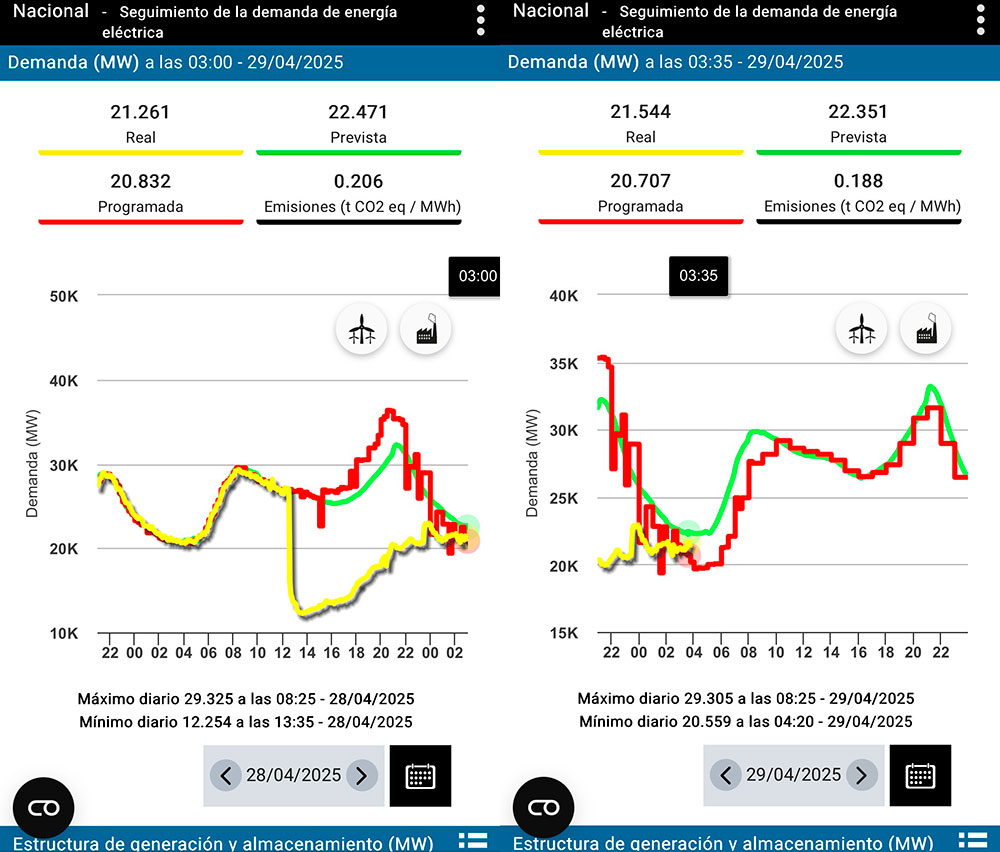

Es lo realmente disruptivo aquí. Tomando de base lo visto con EMIB-M 2.5D en 2023, donde partíamos de un tamaño de retícula de 80x80 mm con hasta 8 módulos HBM y 12 interconexiones EMIB, el año que viene veremos un salto masivo frente a lo que tenemos hoy en el mercado y que es la base del futuro.

En 2026 Intel asegura un salto de retícula de 8x, un package de 120x120 mm con hasta 12 módulos de HBM4 y 20 interconexiones EMIB, lo cual ya es un salto de gigante, pero lo mejor llegará en 2028.

En dicho año el salto frente a 2023 será tremendo, porque el tamaño de la retícula aumentará hasta 12 veces con un área de package de 120x180 mm, pudiendo incluir 24 HBM4E con 38 interconexiones EMIB.

Para entender la comparación con SoW-X de TSMC, los taiwaneses hablan de un tamaño de retícula de 9,5 veces y un área de package de 120x150 mm para finales de 2027. Es decir, Intel va a superar a TSMC no solo en nodos litográficos, sino también en packaging avanzado.

Foveros-R y Foveros-B, dos variantes para atacar a TSMC donde más fuertes son

Lo que tenemos ahora en el mercado es Foveros-S, donde Intel lo ha incluido, por ejemplo, en Meteor Lake y Arrow Lake como arquitecturas generales de sus procesadores, pero también en otros tantos chips más complejos e incluso no lanzados.

Lo que hay que entender aquí es que Foveros-S, aunque usa TSV, apilamiento vertical 3D y es lo más avanzado en este aspecto, realmente es muy complejo y caro de crear entre los Tiles y el Base Tile.

¿Qué pretende Intel ahora? Lanzar dos versiones que se adapten a las necesidades de sus clientes y con ello, presenta Foveros-R y Foveros-B, es decir, Redistribution y Bridge. Sus nombres nos definen bastante bien sus propósitos.

Menores costes o mayor flexibilidad

Foveros-R busca ser la variante económica para aquellos socios que quieran reducir costes manteniendo algunas ventajas, pero perdiendo otras. Por ejemplo, se mantiene un pitch de 25 micrómetros, pero se pierde densidad al no utilizar TSV ni bridge tradicional, pero sí un interposer con RDL. En otras palabras, es un CoWoS de TSMC barato de fabricar con 2.5D como el de los taiwaneses, competencia dura para estos.

Foveros-B, en cambio, quiere dar a los socios de Intel más flexiblidad en el diseño y utiliza para ello un puente de silicio (Silicon Bridge), buscando la interconexión horizontal más simple gracias a dos elementos de nueva factura para esta tecnología: IVR (Internal Voltage Regulator) y condensadores MIM (Metal-Insulator-Metal) como los que usa EMIB-T 2.5D.

Esto permite la conexión de dies lateralmente en diseños modulares a gran escala, y aporta algo que TSMC no tiene: un ratio de rendimiento, densidad y coste mejor al de las soluciones de los taiwaneses. En resumen, Intel busca atacar a TSMC con dos nuevos packaging enfocados en dos principios básicos: una reducción de costes mejorada frente a la competencia, o bien, una flexibilidad de diseño que no está en el mercado en estos momentos.

Foveros Direct 3D: lo más avanzado tecnológicamente del planeta consume 3 veces menos que el packaging actual de las CPU

Sea como fuere, Foveros-R y Foveros-B llegarán al mercado en 2027, por lo que Intel mantendrá Foveros-S como una opción de alto rendimiento, 3D vertical real a mayor coste y con densidad más alta mediante TSV a la espera de estas dos versiones comentadas y de paso, responde a SoW-X con EMIB-T 2.5D con capacidad de apilamiento vertical y soporte para HBM4. Sin olvidar, por supuesto, a Foveros Direct 3D, que es lo más de lo más en bump pitch con Hybrid Bond, una densidad de bumps de 10.000 por mm2 y un consumo C2C de solo 0,05 pJ/bit, algo que TSMC no puede igualar ni ahora ni en el futuro más cercano.

Esto da a las CPU de Intel una ventaja estratégica brutal desde el punto de vista energético, porque una parte importante del consumo de un procesador se está yendo en el packaging. Por contextualizar esto, Arrow Lake consumirá tres veces más con Foveros-S que Nova Lake con Foveros Direct 3D si hablamos del packaging y sin contar el resto de mejoras.

Esto se ve al comparar Meteor Lake (Foveros-S) contra Lunar Lake (Foveros Direct 3D), por ejemplo. Sea como fuere, Intel viene fuerte en este sector y según han mostrado, se impondrán a TSMC sin demasiados problemas, lo cual ya es una locura.

La entrada Intel responde a TSMC y su SoW-X mostrando sus nuevos packaging EMIB-T 2.5D, Foveros-R y Foveros-B, así como Foveros Direct 3D aparece primero en El Chapuzas Informático.